# Eine verlustleistungsoptimierte Dezimator-Architektur für kaskadierte Sigma-Delta Analog-Digital Umsetzer

**M. Becker, K. Heiber, M. Ortmanns, and Y. Manoli**

Lehrstuhl für Mikroelektronik, Albert-Ludwigs-Universität, Georges-Köhler-Allee 102 DG, 79110 Freiburg, Germany

**Zusammenfassung.** Dieser Beitrag stellt einen neuartigen Ansatz einer leistungsfähigen Dezimator-Architektur für kaskadierte Sigma-Delta Modulatoren vor. Die Besonderheit der dargestellten Struktur ist die Integration der Rekombinationslogik kaskadierter Modulatoren und der Korrektur des Verstärkungsfehlers zeitkontinuierlicher (continuous time, CT) Modulatoren in die erste Stufe des Dezimators. Der Entwurf einer passenden Filtertopologie wird abgeleitet, analysiert und durch Simulationen verifiziert. Die vorgeschlagene Struktur wird mit einer herkömmlichen Implementierung verglichen. Das Ergebnis dieses Vergleiches ist eine Verbesserung der Effizienz um Dekaden.

## 1 Einleitung

$\Sigma\Delta$ -Modulatoren sind gut dazu geeignet, eine robuste analog-digital Wandlung zu erzielen. In letzter Zeit wurden systematische Untersuchungen zur erreichbaren Leistungsfähigkeit vorgestellt (Marques et al., 1998). Prinzipiell wird das vom Quantisierer stammende Quantisierungsrauschen durch die Überabtastung unterdrückt, zusätzlich zu höheren Frequenzen hin geformt und anschließend durch den Dezimator digital Tiefpass gefiltert. Bei den meisten in der Vergangenheit durchgeföhrten Untersuchungen und entwickelten Konzepten von  $\Sigma\Delta$ -Modulatoren wurden zeitdiskrete (discrete time, DT) Realisierungen betrachtet (Marques et al., 1998) und in Switched-Capacitor (SC) Technik implementiert. In der letzten Zeit wurde zeitkontinuierlichen  $\Sigma\Delta$ -Modulatoren aus unterschiedlichen Gründen vermehrt Aufmerksamkeit gewidmet. Sie zeichnen sich z. B. durch die mögliche höhere Abtastrate bei gleichem Leistungsverbrauch, durch ein geringeres thermisches Rauschen und ein implizites Anti-Aliasing Filter (Cherry und Snelgrove, 1999) aus. Auf der anderen Seite sind CT Modulatoren schwieriger zu entwerfen und es müssen verschiedene Nichtidealitäten

der integrierten Komponenten von CT Filtern beachtet werden (Cherry und Snelgrove, 1999; Ortmanns et al., 2001a). Heutzutage exisitiert ein steigender Bedarf an sehr hohen Umsetzraten, wie z. B. in Telekommunikationsanwendungen, wodurch eine Abtastrate der Modulatoren im Bereich oberhalb 100 MHz bedingt ist. Aber wenn die Umsetzrate erhöht wird, muss ab einem bestimmten Punkt die Überabtastung (oversampling ratio,  $OSR$ ) reduziert werden, um die Abtastfrequenz (sampling frequency,  $f_S$ ) des Systems innerhalb realistischer Grenzen zu halten. Dies ist u. a. auch bedingt durch den enorm ansteigenden Leistungsverbrauch des Analogteils bei dieser sehr hohen Geschwindigkeit und darüber hinaus auch wegen des Einflusses des Dezimators auf dem selben Chip. Mittlerweile sind kaskadierte  $\Sigma\Delta$ -Modulatoren eine bekannte Alternative, um A/D Umsetzer höherer Ordnung und hoher Auflösung zu implementieren, und dabei nicht eine Skalierung aufgrund der möglichen Instabilität in Kauf zu nehmen und ohne einen sehr linearen multi-bit D/A Wandler in der Rückkopplung zu benötigen. Andererseits zeigen kaskadierte CT Implementierungen eine ausgeprägte Abhängigkeit von RC-Toleranzen. Eine Korrektur dieses Effektes ist zwar möglich, resultiert jedoch in einem Ausgangsdatenstrom hoher Wortbreite (Ortmanns et al., 2001b). Wird die digitale Seite eines Umsetzers betrachtet, fällt auf, dass der Einfluss des Dezimators auf den Leistungsverbrauch des kompletten A/D Wandlers ebenfalls ansteigt. Der Dezimator ist eine wichtige Komponente aber die meisten Veröffentlichungen konzentrieren sich eher auf den Analogteil eines Umsetzers, d. h. auf den Modulator. Nichtdestoweniger kann der Anteil des Dezimators am Leistungsverbrauch des Wandlers keineswegs vernachlässigt werden. Daher fordert der Bedarf an verlustleistungsarmen Implementierungen – aber auch Effekte wie Substratrauschen und Rauschen bedingt durch die Schaltvorgänge – Anpassungen und auch Optimierungen des Dezimators. Ein wichtiges Entwurfs- und Effizienzkriterium ist, möglichst single-bit Eingänge für den Dezimator zu erhalten, der bei hoher Geschwindigkeit operieren muss, bevor die Abwärtsabtastung stattfindet. Jedoch ist dies für kaskadierte und insbesondere

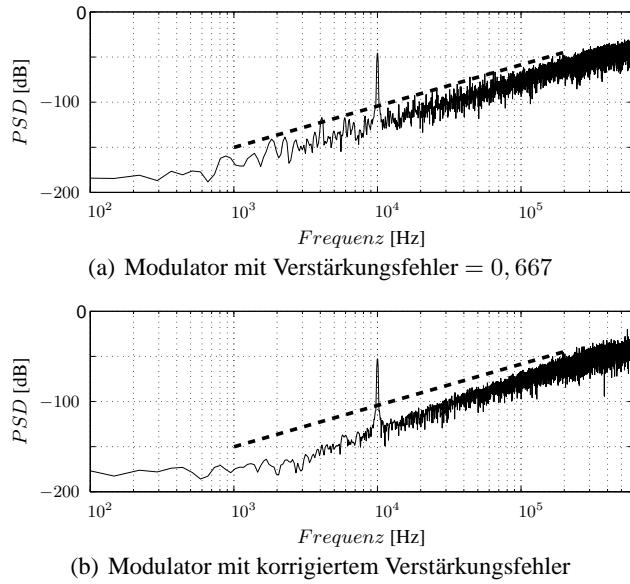

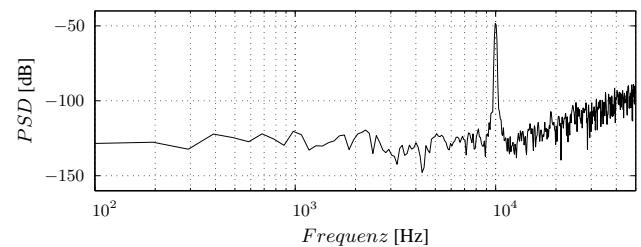

**Abbildung 1.** Leistungsdichtespektren am Ausgang eines  $\Sigma\Delta$ -Modulators.

für CT kaskadierte Modulatoren nicht gegeben (Medeiro et al., 1998). Dieser Beitrag schlägt folglich einen optimierten Dezimator vor und leitet eine Architektur für kaskadierte (DT und CT) Modulatoren her. Es wird gezeigt, dass es möglich ist, die Digitallogik, welche in kaskadierten  $\Sigma\Delta$ -Modulatoren benötigt wird, in den Dezimator zu verlagern bzw. in diesen zu integrieren. Auf diese Art und Weise kann der Leistungsverbrauch und die Komplexität der Schaltung des kompletten A/D Umsetzers drastisch reduziert werden.

## 2 Kaskadierte $\Sigma\Delta$ -Modulatoren

Die Leistungsfähigkeit von einstufigen Modulatoren einer Ordnung größer als zwei ist wesentlich niedriger als im Idealfall (Marques et al., 1998). Auf der anderen Seite stellt die Verbesserung der Auflösung mittels interner multi-bit Quantisierer strenge Anforderungen an die Linearität der multi-bit digital-zu-analog Umsetzer (DAC) in der Rückführung des Modulators (Norsworthy et al., 1997; Marques et al., 1998). Daher wurden kaskadierte Architekturen für  $\Sigma\Delta$ -Modulatoren entwickelt, und in den letzten Jahren wurden viele Entwürfe präsentiert. Die meisten dieser kaskadierten oder mehrstufigen Topologien basieren auf stabilen Modulatoren erster und zweiter Ordnung. Sie bieten Möglichkeiten, ein fast ideales Noise-Shaping höherer Ordnung zu erreichen, auf Kosten einer höheren Empfindlichkeit gegenüber den Nichtidealitäten der einzelnen Bausteine (Medeiro et al., 1998). Die Ausgänge werden dann in eine digitale Rekombinationslogik eingespeist, die die Wortbreite des Modulator-Gesamtausgangs auf mehrere Bit vergrößert (Medeiro et al., 1998; Ortmanns et al., 2001a). Das bedeutet, dass die erste Dezimationsstufe Multiplikationen

mit Operanden hoher Wortbreite anstatt simpler Additionen durchführen muss.

Üblicherweise wird eine  $\Sigma\Delta$ -A/D-Umsetzung als zeitdiskretes System implementiert, weil die Filter einfacher zu entwerfen sind und wegen des hohen Grades an Linearität der resultierenden Schaltungen. Es wurde aber ebenfalls gezeigt (Ortmanns et al., 2001a), dass kaskadierte CT Modulatoren entworfen werden können, die die gleiche Leistungsfähigkeit aufzeigen wie ihre zeitdiskreten Pendants. Diese Modulatoren funktionieren mit der gleichen digitalen Rekombinationslogik wie zeitdiskrete Systeme (Marques et al., 1998). Für die Implementierung kaskadierter CT Modulatoren mit hoher Auflösung müssen verschiedene Aspekte berücksichtigt werden, die die Leistungsfähigkeit einschränken. Eine Methode, um den Verstärkungsfehler zu kompensieren, wird in (Ortmanns et al., 2001b) vorgestellt: Jeglicher Verstärkungsfehler in den Integratoren der ersten Stufe kann beseitigt werden, indem der Ausgangsdatenstrom des zweiten Quantisierers durch das Quadrat dieses Fehlerwertes dividiert oder der des ersten Quantisierers damit multipliziert wird (siehe Abb. 1a). Der Verstärkungsfehler vermindert die Ordnung des Noise Shapings, wie in Abb. 1 für einen SOFO-Modulator ( $OSR = 24$ , Verstärkungsfehler =  $2/3$ ) (Ortmanns et al., 2001b) dargestellt ist. In dieser Abbildung zeigt nur die Version mit Korrektur – durch Multiplikation des Ausgangssignales mit einem ca. 8 Bit Korrekturwort – ein perfektes Noise Shaping dritter Ordnung. Diese Korrektur resultiert aber in einem Modulator-Ausgangsdatenstrom und damit auch einem Dezimator-Eingangssignal hoher Wortbreite.

Folglich wäre die Hardwarekomplexität und der Leistungsverbrauch eines konventionellen Dezimators enorm. Wie im nächsten Abschnitt gezeigt wird, ist es vorteilhaft, die Fehlerkorrektur vom Eingang des Dezimators in das Innere der Struktur zu transferieren, und somit zu einer verbesserten Leistungsfähigkeit zu gelangen.

## 3 Vorgeschlagene Dezimator Struktur

### 3.1 Herkömmliche Dezimator Architekturen

In den meisten Fällen wandelt ein  $\Sigma\Delta$ -Modulator ein analoges Eingangssignal  $x(t)$  in ein überabgetastetes digitales Signal  $s(n)$ . Hierbei wird das Quantisierungsrauschen zu höheren Frequenzen hin geformt. Das Signal  $s(n)$  wird anschließend im Dezimator zur gewünschten Auflösung und Abtastrate digital gefiltert. Im Allgemeinen wird dieser Prozess – basierend auf dem Nyquist-Theorem und der digitalen Filtertheorie – in mehrere Stufen von Tiefpassfilterung und Herabtastung aufgeteilt (Norsworthy et al., 1997).

Zur Realisierung eines Dezimators existieren viele unterschiedliche Design-Alternativen mit einer Vielzahl von Parametern, die in einem sehr komplexen Zusammenhang stehen. Eine gebräuchliche Struktur ist z. B. ein Filter mit endlicher Impulsantwort (sog. FIR-Filter) in der ersten Dezimationsstufe, gefolgt von steilflankigeren Filtern (Norsworthy et al.,

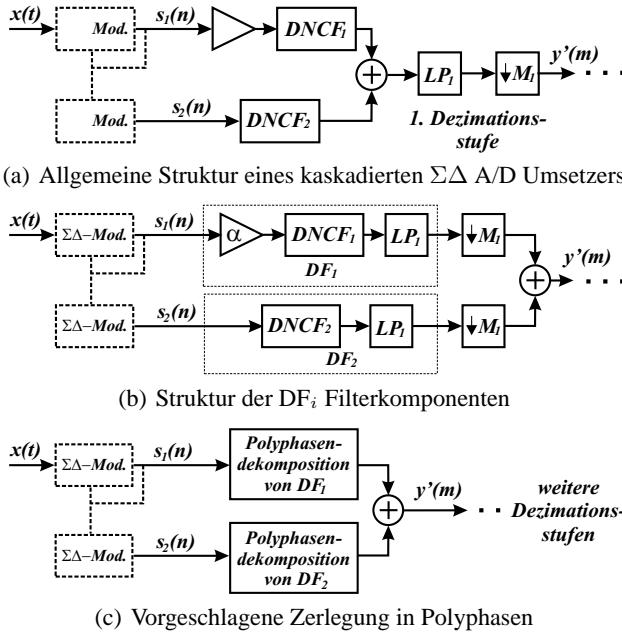

Abbildung 2. Evolution der Dezimator-Topologien.

1997), wobei die bevorzugte Architektur ein single-bit Eingangssignal hat. Dies ist aber, wie oben erläutert, üblicherweise bei kaskadierten Modulatoren nicht gegeben.

Der Fokus dieses Beitrages ist nun ein erweitertes Polyphasenfilter in der ersten Dezimatorstufe, das die Rekombinationslogik wie auch eine digitale Korrektur miteinbezieht. Auf diese Weise werden single-bit überabgetastete Eingangssignale  $s_i(n)$  in den Dezimator eingespeist.

### 3.2 Integration der Rekombinationslogik und der Korrektur des Verstärkungsfehlers in die erste Dezimatorstufe

In Abb. 2a ist die herkömmliche Struktur eines zweistufigen  $\Sigma\Delta$  A/D Umsetzers gezeigt. Er besteht aus:

- Zwei  $\Sigma\Delta$ -Modulatoren mit Rekombinationslogik (Digital Noise Cancellation Filters DNCF<sub>1</sub> und DNCF<sub>2</sub>) nach (Marques et al., 1998),

- dem 8 Bit Faktor  $\alpha$  zur Korrektur des Verstärkungsfehlers im Fall einer CT Implementierung (Ortmanns et al., 2001b),

- der ersten Dezimatorstufe, bestehend aus einem Tiefpassfilter LP<sub>1</sub> und einer Herabtastung um einen Faktor  $M_1$ ,

- weiteren Dezimatorstufen (hier nicht gezeigt).

In (Li und Wetherrell, 2000) wird eine FIR-Sinc Architektur eingeführt, die sich eine niedrige Anzahl an Bits am Eingang des Dezimators zu Nutze macht. Dies wird erreicht, indem die Rekombinationslogik an den Ausgang der ersten Dezimatorstufe verschoben wird, und dadurch eine niedrige Anzahl an Eingangsbits im Dezimatorfilter bewahrt.

Wie aus Abb. 2b ersichtlich ist, erweitern wir diesen Ansatz, um DNCF<sub>1</sub>, DNCF<sub>2</sub> und selbst die digitale Korrektur des Verstärkungsfehlers komplett in zwei neue Digitalfilter DF<sub>1</sub> und DF<sub>2</sub> zu integrieren. Dies ist ein Zwischenschritt in Richtung der vorgeschlagenen neuen Dezimatorstruktur.

Nun wird die konzeptionelle Ableitung dieser Filter erläutert. Zunächst wird das Antialiasing- (Tiefpass-) Filter  $H_{LP_1}(z)$  der ersten Dezimatorstufe nach den klassischen Kriterien für digitale Tiefpassfilter entworfen (Norsworthy et al., 1997). Aus den Frequenzgängen  $H_{DNCF_i}(z)$  (spezifiziert in (Marques et al., 1998)) für  $i \in \{1, 2\}$  und der Übertragungsfunktion  $H_{LP_1}(z)$  des Tiefpasses, können dann die Grundgleichungen für die Filter  $H_{DF_i}(z)$  gewonnen werden:

$$H_{DF_i}(z) = H_{DNCF_i}(z) \cdot H_{LP_1}(z) \quad (1)$$

Wird ein kaskadierter CT  $\Sigma\Delta$ -Modulator eingesetzt, so wird zusätzlich der Faktor  $\alpha$  für die Korrektur des Verstärkungsfehlers in  $H_{DNCF_1}(z)$  eingerechnet. Somit lauten die Gleichungen bei Verwendung von CT Modulatoren:

$$H_{DF_{1,CT}}(z) = \alpha \cdot H_{DNCF_1}(z) \cdot H_{LP_1}(z) \quad (2)$$

$$H_{DF_{2,CT}}(z) = H_{DNCF_2}(z) \cdot H_{LP_1}(z) \quad (3)$$

Die neuen Koeffizienten für die Filter DF<sub>i</sub> können dann durch die entsprechende Faltung erhalten werden:

$$h_{DF_i}(n) = \sum_{k=-\infty}^{\infty} h_{DNCF_i}(k) \cdot h_{LP_1}(n-k) \quad (4)$$

### 3.3 Polyphasenzerlegung

Im Abschnitt 1 wurde bereits der steigende Bedarf an sehr hohen Umsetzraten angedeutet. Werden jedoch die Umsetzraten immer weiter erhöht, so muss die Überabtastrate OSR herabgesetzt werden, um die Abtastfrequenz  $f_S$  des Systems innerhalb realistischer Grenzen zu halten (Medeiro et al., 1998). Für die bei hoher Frequenz operierende Eingangsstufe des Dezimators ist die Verwendung von sinc<sup>K</sup>-Filtern geeignet und auch leistungseffizient, aber eher beschränkt auf Modulatoren mit hohem OSR (Norsworthy et al., 1997). Auf Grund von sinkenden Überabtastraten moderner  $\Sigma\Delta$ -Modulatoren, ist die Verwendung der Polyphasen-Dekomposition eine effektivere Alternative (Norsworthy et al., 1997). Nachteilig für sinc-Filter ist des Weiteren die Notwendigkeit einer zusätzlichen Filterstufe zur Korrektur der Übertragungsfunktion (Norsworthy et al., 1997).

Allgemeinere Gründe für die Verwendung von FIR-Polyphasenfiltern in der ersten Stufe des Dezimators sind zum einen die Berechnungen, die so bei niedrigerer Frequenz durchgeführt werden können (Norsworthy et al., 1997), sowie Einsparungen an Speicher. Somit gewährleistet diese Struktur eine bessere Recheneffizienz (vgl. hierzu Abschnitt 4). Dies ist eine Folge der Tatsache, dass die (implizite) Dezimation in Polyphasenstrukturen vor der Tiefpassfilterung stattfindet.

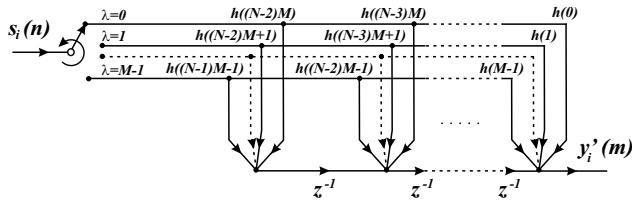

Abbildung 3. Ein Zweig der Polyphasenzerlegung.

Ausgehend von Gl. 1, kann die Polyphasen-Dekomposition von  $H_{DF_i}(z)$  durchgeführt werden mittels

$$H_{DF_i}(z) = \sum_{\lambda=0}^{M_1-1} z^{-\lambda} \cdot H_{\lambda}(z^{M_1}) \quad (5)$$

wobei  $M_1$  die Abwärtstastung der ersten Dezimationsstufe ist und  $h_{\lambda}(m) \circ \bullet H_{\lambda}(z)$  die Koeffizienten der verschiedenen Phasen  $\lambda$  sind.

Um zu verhindern, dass die Multiplikation mit dem Korrekturfaktor  $\alpha$  von CT Modulatoren bei hoher Taktrate durchgeführt werden muss, schlagen wir vor, diese Operation in das Polyphasenfilter einzubinden. Dies wird erreicht durch eine Multiplikation der Koeffizienten  $h_{DF_1}(n)$  mit dem Faktor  $\alpha$ . In diesem Fall werden gemäß Gl. 4 die  $h_{DF_i}(n)$  vor der Polyphasen-Dekomposition bestimmt durch

$$h_{DF_1,CT}(n) = \alpha \sum_{k=-\infty}^{\infty} h_{DNCF_1}(k) \cdot h_{LP_1}(n-k) \quad (6)$$

$$h_{DF_2,CT}(n) = \sum_{k=-\infty}^{\infty} h_{DNCF_2}(k) \cdot h_{LP_1}(n-k) \quad (7)$$

### 3.4 Gesamtaufbau der vorgeschlagenen Dezimator-Architektur

In Abb. 2c ist die Struktur der ersten Stufe der neuen Dezimatorstruktur gezeigt. Sie besteht aus Polyphasenfiltern – mit single-bit Eingängen – in zwei parallelen Zweigen, die die digitale Rekombinationslogik für kaskadierte Modulatoren beinhalten, und für den Fall eines CT Modulators zusätzlich die Korrektur des Verstärkungsfehlers. Der Ausgang der Polyphasenstruktur ist an ein Halbbandfilter der nächsten (letzten) Stufe angeschlossen, um steilflankig an der Kante des Basisbandes zu filtern. In Abb. 3 ist ein Zweig der transponierten Polyphasen-Dekomposition mit Filterkoeffizienten und der Verzögerungskette im Detail zu sehen (Norsworthy et al., 1997).

## 4 Simulationsergebnisse

### 4.1 Verifikation des vorgestellten Dezimators

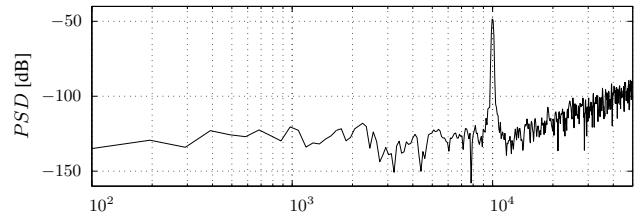

In Abb. 4 sind die Leistungsdichtespektren nach der ersten Dezimationsstufe einer konventionellen Struktur (Fig. 4a) und der hier vorgeschlagenen Polyphasenarchitektur (Fig. 4b) zum Vergleich dargestellt. Die Diagramme wurden mittels Simulation für einen CT SOFO Modulator (mit

(a) Herkömmliche Dezimation (vgl. Abb. 2(a))

(b) Vorgeschlagene Dezimation (vgl. Abb. 2(c))

Abbildung 4. Leistungsdichtespektrum einer herkömmlichen und der vorgeschlagenen neuen Dezimation (jeweils nach der ersten Dezimationsstufe).

Tabelle 1. Zusammenstellung der Simulationsparameter.

| Parameter                             | Wert       |

|---------------------------------------|------------|

| Signalfrequenz $f_{Signal}$           | 10 kHz     |

| Bandbreite $f_B$                      | 25 kHz     |

| Überabtastung $OSR$                   | 24         |

| Abtastfrequenz $f_S$                  | 1,2 MHz    |

| Stoppband-Unterdrückung               | -90 dB     |

| Abwärtstastung $M_1$ der ersten Stufe | 12         |

| $IBN$ des Modulatorausgangs           | -74, 15 dB |

| $IBN$ nach der ersten Stufe           | -72, 39 dB |

$OSR = 24$ , Verstärkungsfehler =  $2/3$ ,  $\alpha = (2/3)^2$  mit Parametern wie in Tab. 1 ermittelt. Es kann klar erkannt werden, dass die Diagramme nahezu identisch sind und damit die Funktionalität und Korrektheit des neuen Ansatzes zeigen.

### 4.2 Recheneffizienz der vorgeschlagenen Struktur

In Tab. 2 wird eine Abschätzung des Rechenaufwandes pro Sample für den Ausgang  $y'(m)$  der ersten Dezimationsstufe für die Strukturen aus Abb. 2a und c gezeigt. Angegeben sind dabei die geschätzte Anzahl der jeweiligen Rechenoperationen, sowie die Wortbreite der Operanden für Additionen und Multiplikationen. Für die konventionelle Struktur aus Abb. 2a setzen sich die Werte unter FIR zusammen aus den Beiträgen, die zum einen von der Rekombinationslogik (RL) und zum anderen von der Tiefpassfilterung (LP, Ordnung 130) stammen. Die Zeilen in Tab. 2, die mit PP bezeichnet sind, enthalten die Abschätzungen für die vorgeschlagene optimierte Polyphasen-Dekomposition (Fig. 2c), die Rekombinationslogik, Verstärkungsfehler-Korrektur und

**Tabelle 2.** Abschätzung der Recheneffizienz.

| Struktur | Add.                         | Mult.                     | Shifts        |

|----------|------------------------------|---------------------------|---------------|

| FIR      | RL 48 (8 Bit)                | 12 ( $1 \times 8$ Bit)    | 36 (8 Bit)    |

|          | LP 1572 (16 Bit)             | 1584 ( $9 \times 11$ Bit) | 1572 (16 Bit) |

| PP       | PP <sub>1</sub> 134 (16 Bit) | 135 ( $1 \times 11$ Bit)  | 134 (16 Bit)  |

|          | PP <sub>2</sub> 133 (16 Bit) | 134 ( $1 \times 11$ Bit)  | 133 (16 Bit)  |

Tiefpassfilter umfasst. Der gesamte Rechenaufwand, der in Abb. 2c gezeigten Struktur, ist durch die Summe der jeweiligen Werte in Tab. 2 gegeben.

Wie aus Tab. 2 ersichtlich ist, wird durch die vorgeschlagene Architektur der Rechenaufwand erheblich reduziert und damit die Effizienz verbessert. Bei Betrachtung der notwendigen Additionen von 16 Bit Operanden, ist die Effizienz des neuen Ansatz um einen Faktor sechs besser. Die Anzahl der Multiplikationen wird ebenfalls auf ein sechstel reduziert im Vergleich zur herkömmlichen Realisierung. Aber bemerkenswerter an dem neuen Ansatz ist, dass lediglich  $1 \times 11$  Bit anstatt  $9 \times 11$  Bit Operationen durchgeführt werden müssen, was in einer Effizienzsteigerung um einen Faktor 80 resultiert.

Wird der neue Ansatz mit einer üblichen Polyphasen-Dekomposition (also ohne integrierte Rekombinationslogik und Verstärkungsfehler-Korrektur) realisiert, so kann die Anzahl der Operationen ebenfalls um einen Faktor sechs reduziert werden. Die Wortbreite bei den Multiplikationen verringert sich in diesem Fall jedoch nicht, und somit würde sich insgesamt nur eine geringfügige Effizienzsteigerung ergeben.

## 5 Erweiterung und Ausblick

Die vorgeschlagene Polyphasen-Dezimatorarchitektur kann für die Anwendung in kaskadierten  $\Sigma\Delta$ -Modulatoren mit multi-bit Ausgängen erweitert werden. Darüber hinaus ist eine Einbindung der digitalen Korrektur von Nichtlinearitäten (Norsworthy et al., 1997) eine interessante Aufgabenstellung, die näher untersucht werden wird.

## 6 Zusammenfassung

Es wurde eine optimierte Dezimatorstruktur für kaskadierte zeitdiskrete und zeitkontinuierliche  $\Sigma\Delta$ -Modulatoren vorgestellt. Der betrachtete Ansatz macht vornehmlich Gebrauch von der sinkenden Überabstrate (*OSR*) moderner  $\Sigma\Delta$ -Modulatoren und stellt damit eine effiziente Alternative zu herkömmlichen Dezimatorarchitekturen dar. Die komplette Rekombinationslogik kaskadierter Modulatoren wurde zusammengefasst und in den neuen Ansatz eingebunden. Wenn zeitkontinuierliche Modulatoren eingesetzt werden, kann desweiteren die notwendige Korrektur des Verstärkungsfehlers der Integratoren in die erste Dezimationsstufe integriert werden.

Die Architektur wurde durch MATLAB<sup>TM</sup>-Simulationen verifiziert. Zum Abschluss wurde die niedrigere Komplexität der neuen Struktur im Vergleich zu herkömmlichen Realisierungen durch eine Abschätzung des Rechenaufwandes gezeigt.

## Literatur

- Cherry, J. A. und Snelgrove, W. M.: CT Delta-Sigma Modulators for High-Speed A/D Conversion, Kluwer Academic Publishers, 1999.

- Li, S.-F. und Wetherrell, J.: A Compact Low-Power Decimation Filter for Sigma Delta Modulators, ICASSP, 6, 3223–3226, 2000.

- Marques, A., Peluso, V., Steyaert, M. S. und Sansen, W. M.: Optimal Parameters for Delta-Sigma Modulator Topologies, IEEE Trans. on Circuits and Systems II, 45, 1232–1241, 1998.

- Medeiro, A., Pérez-Verdú, A. und Rodríguez-Vázquez, A.: Top-Down Design of High-Performance  $\Sigma\Delta$  Modulators, Kluwer Academic Publishers, 1998.

- Norsworthy, S. R., Schreier, R. und Temes, G. C.: Delta-Sigma Data Converters – Theory, Design, and Simulation, IEEE Press, 1997.

- Ortmanns, M. M., Gerfers, F. und Manoli, Y.: On the Synthesis of Cascaded CT  $\Sigma\Delta$  Modulators, ISCAS, V419–V422, 2001a.

- Ortmanns, M., Gerfers, F., Samid, L. und Manoli, Y.: Successful Design of Cascaded CT  $\Sigma\Delta$  Modulators, ICECS, 321–324, 2001b.