# Advances in Radio Science

# Eine FPAA-Architektur zur rekonfigurierbaren Instantiierung von zeitkontinuierlichen Analogfiltern

#### J. Becker and Y. Manoli

Lehrstuhl für Mikroelektronik, IMTEK, Albert-Ludwigs-Universität, 79110 Freiburg, Germany

Zusammenfassung. Im Folgenden wird eine neue Methodik von FPAAs (Field Programmable Analog Arrays) gezeigt, die speziell für die Instantiierung von zeitkontinuierlichen (continuous-time, CT) Analogfiltern in Hardware entwickelt wurde. Die Chiptopologie beinhaltet 17 digital konfigurierbare analoge Blöcke (configurable analog blocks, CABs), die durch ein hexagonales Netzwerk miteinander verbunden sind. Jeder CAB ist aus einstellbaren G<sub>m</sub>-C Integratoren aufgebaut, welche das analoge Signal sowohl formen und seinen Weg durch die Matrix festlegen, gleichzeitig aber auch die Grundbausteine für zeitkontinuierliche Hochfrequenzfilter darstellen. Intelligente Pufferspeicher für die Ein-/Ausgänge (IO-buffer) garantieren die Rekonfigurierung der Matrix mit minimaler Störung des kontinuierlichen Analogsignals. Die Architektur wird als Hardwareplattform für beliebige Schaltungen, welche aus einer gegebenen Anzahl an  $G_m$ -C-Zellen bestehen, eingeführt und verifiziert bevor eine exemplarische Instantiierung eines Butterworth Filters 4. Ordnung in Biquad Anordnung gezeigt wird.

# 1 Einleitung

FPAAs haben in der Vergangenheit Verwendung als Eingangsstufen analoger Signalverarbeitung gefunden und werden üblicherweise auch als Schnittstelle zum Auslesen von Sensoren verwendet. Adaptive Filter werden gebraucht, wenn die Signalbandbreite oder die Datenrate eines Eingangssignals veränderlich ist, z.B. beim Auslesen von Festplatten oder in der Funktechnik. Andere Anwendungen, die nach rekonfigurierbaren Architekturen verlangen, sind selbstheilende und redundante Schaltungen für Umgebungen, in denen die Funktionsfähigkeit garantiert werden muss, wenn Teile der Schaltung zerstört werden und nicht ausgetauscht werden können. Die vorliegende Arbeit konzentriert sich auf adaptive Filter mit digitaler Einstellbarkeit und niedrigen Anforderungen an die Linearität für rekonfigurierbare Hochfrequenzdatenerfassung.

Es gibt viele Ansätze für rekonfigurierbare analoge Bausteine von denen die Mehrzahl in Schalter-Kondensator-

Correspondence to: J. Becker (jobeck@imtek.de)

Technik (switched-capacitor) entwickelt wurden. Der Leistungsverbrauch von zeitkontinuierlichen (CT) Designs kann aber weniger als ein Drittel von zeitdiskreten (discretetime, DT) Realisierungen betragen. Beim Einsatz in Filtern übertreffen CT-Designs die DT-Designs nicht nur um das Zehnfache an Bandbreite, es wird außerdem kein vorangestellter Antialiasing-Filter benötigt (Becker and Manoli, 2004). Schließlich beinhalten CT-FPAAs nur quasi-statische Schalter und haben keine hochfrequenten Schaltvorgänge, was sie für den Einsatz in empfindlichen analogen Schaltkreisen empfiehlt.

Ziel dieser Arbeit ist es, eine rekonfigurierbare Hardwareplattform für Hochfrequenzfilter zu erstellen, die in den gleichen CMOS-Prozessen wie Analog-Digital-Wandler und digitale Logik realisiert werden kann um dem stetigen Bedarf an höherer Integration zu genügen. Aus Gründen des geringen Leistungsverbrauchs, Antialiasing und Verringerung des Schalterrauschens ist es wünschenswert, die Vorteile von rekonfigurierbaren analogen Schaltungen durch digital konfigurierbare analoge Blöcke zu erreichen, die in zeitkontinuierlicher Technik hergestellt werden. Es scheint vielversprechend, Rekonfigurationstechniken für gemischt ana- $\log/\text{digitale}$  Bausteine mit modernen  $G_m$ -C Filtern zu kombinieren, um eine rekonfigurierbare CT-Architektur zu erreichen, die an Filterspezifikationen (Bandbreite, Linearität) und Umgebungsbedingungen (Leistung, Eingangssignal) anpassbar ist.

#### 2 Design eines CABs für CT-Filter

Das genaue Design der CABs hängt hauptsächlich vom Verwendungszweck des FPAAs ab und gegenwärtige Realisierungen reichen von Architekturen mit einer kleinen Anzahl von komplexen CABs bis zu großen Arrays mit sehr einfachen CABs. Moderne Umsetzungen von zeitkontinuierlichen Hochfrequenzfiltern können ohne Widerstände oder Spulen gebaut werden, falls Transkonduktanzverstärker und Kapazitäten verwendet werden (Nauta, 1992). Diese Designs sind nicht nur platzsparend sondern Filter, die aus G<sub>m</sub>-C-Integratoren aufgebaut sind, können außerdem ohne Rückkopplung auskommen und sind deswegen sehr schnell.

Der hier verwendete Transkonduktanzverstärker basiert auf einer Methode für digital konfigurierbare  $G_m$ -Zellen in Hochfrequenzfiltern (Pavan and Tsividis, 2000). Ein Einheitstranskonduktanzverstärker besteht aus einem differentiellen Transistorpaar mit aktiver Last. Die Quellen, welche den Strom für die Transistoren liefern, können von einem digitalen Eingang ein- und ausgeschaltet werden. Wenn das "arbeitende" Paar ausgeschaltet ist, wird ein anderes "Ersatz"-Paar (dummy) zwischengeschaltet um die parasitäre Eingangskapazität des "Ein-Zustandes" anzupassen.

Ein digital einstellbarer Transkonduktanzverstärker kann durch eine Parallelschaltung von solchen Einheitstranskonduktanzverstärkern erreicht werden. Schrittweite, Minimum und Maximum können durch Größe und Anzahl der  $g_m$ s festgelegt werden. Eine einstellbare  $G_m$ -Zelle mit einem 3-Bit Programmierwort (8 Zwischenschritte von 0 bis zum Maximum) kann, wie in (Pavan and Tsividis, 2000) sowie (Becker and Manoli, 2004) gezeigt, durch binär gewichtete Einheitstranskonduktanzen erreicht werden. Für eine genauere Beschreibung dieser Bausteine auf Schaltungsebene sei der Leser auf (Becker and Manoli, 2004) verwiesen.

Die vorgeschlagene konfigurierbare  $G_m$ -Zelle kann in statischen Filterstrukturen verwendet werden und erlaubt das Einstellen einzelner Stufen einer festen Architektur (Pavan and Tsividis, 2000). Der Vorteil von FPAAs ist aber die Möglichkeit, Schaltungsstrukturen zu verändern. Daher präsentieren wir eine neue Architektur von rekonfigurierbaren Bausteinen, die aus digital einstellbaren  $G_m$ -Zellen bestehen, welche eine Instantiierung von Hochfrequenzfiltern, gebaut aus  $G_m$ -C Integratoren, erlauben. Die Neuheit ist, dass die Filterstrukturen voll rekonfigurierbar sind und ihren Vorteil aus den charakteristischen Eigenschaften der vorgeschlagenen einstellbaren  $G_m$ -Zellen ziehen.

#### 3 Rekonfigurierbare Signalwege

Zunächst müssen Blöcke entwickelt werden, welche die einzelnen  $G_m$ -Zellen verbinden und zwar so, dass sie die Bandbreite nicht verringern. Die Neuheit des vorgestellten CABs ist es, das Prinzip eines schaltbaren Einheitstranskonduktanzverstärkers nicht nur für parallele Verbindungen, sondern auch für einen Multiplexer ohne Übertragungsschalter im Signalpfad zu benutzen (Becker and Manoli, 2004). Da die selben Verstärker für das Verbinden und Einstellen der Zellen verwendet werden, gibt es keine weiteren Komponenten, welche die Bandbreite verringern. Daher definiert allein das Design der Transkonduktanzverstärker die Gesamtbandbreite des Filters.

Damit jede mögliche Filterstruktur realisiert werden kann, muss jede Kombination von  $G_m$ -Zellen grundsätzlich möglich gemacht werden: serielle und parallele Verbindungen, Invertierung des differentiellen Signals und Rückkopplungsschleifen jeglicher Ordnung. Signallenkung ist eine wesentliche Anforderung an ein FPAA, da es der einzige Weg ist, Information von einem Punkt zu einem anderen auf dem Chip zu transportieren. Serielle Verbindungen

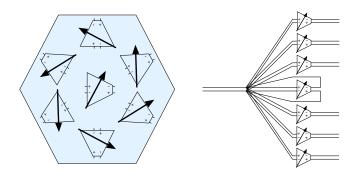

Abbildung 1. Struktureller Überblick eines hexagonalen CAB.

sind die Basis für den Signalverlauf und sind trivial für jede Matrixanordnung, solange jede Zelle Daten an ihre unmittelbaren Nachbarn weitergeben kann und Signalpfade sich nicht kreuzen. Wenn kein zusätzliches übergeordnetes Verbindungsnetzwerk angelegt werden soll, können in einem homogenen zweidimensionalen Feld parallele Verbindungen zweifach angelegt werden, was für den gewünschten Zweck ausreichend ist. Deswegen sind die Rückkopplungsmöglichkeiten des Netzwerkes die entscheidenden Kriterien für die Feldstruktur.

Die einfachste Struktur, die alle Rückkopplungsordnungen erlaubt, ist das hexagonale Layout (Stojmenovic, 1997). Zusätzlich muss für die Rückkopplung auf sich selbst eine interne Verbindung hinzugefügt werden. Abbildung 1 zeigt ein komplettes CAB mit sieben Zweigen, dessen Eingangssignale mit einem Knoten verbunden sind.

Der einstellbare Transkonduktanzverstärker enthält sowohl die Verbindungen zu den sechs Nachbar-CABs als auch die Rückkopplung zum Eingangsknoten. Da ein invertierender und ein nichtinvertierender Ausgang gebraucht werden, besteht jeder Transkonduktor in diesem Bild aus zwei drei-Bit parallel geschalteten  $G_m$ -Zellen; eine für den invertierenden und eine für den nichtinvertierenden Ausgang. Folglich wird das wirkende  $G_m$  durch ein 4-bit Programmierwort ausgewählt (1 Bit invertieren, 3 Bit einstellen). Wenn ein Verstärker ausgeschaltet ist, ist nur die parasitäre Eingangskapazität an diesem Knoten aktiv. Wenn er eingeschaltet ist, bleibt die Eingangskapazität die Gleiche und die  $G_m$ -Zelle bildet zusammen mit der Eingangskapazität der Nachbarzelle eine  $G_m$ -C Stufe des Filters.

#### 4 Chipstruktur

Mit den Bausteinen, die im vorangegangenen Abschnitt beschrieben wurden, ist es nun möglich homogene netzwerkartige Feldanordnungen zu bauen.

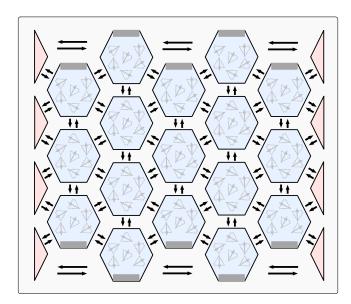

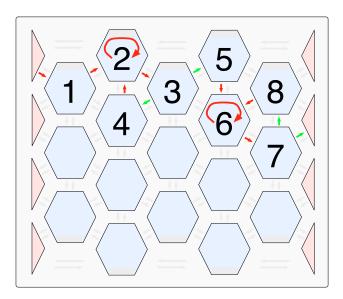

Wie in Abb. 2 beschrieben, verbinden bidirektionale Signale jeden CAB lokal mit seinen Nachbarn, wobei die Verbindungsmöglichkeiten in den CABs enthalten sind. Jeder Ausgangszweig ist mit dem Eingangsknoten der jeweiligen Nachbarzelle verbunden und deswegen ist es möglich, Signale durch den Chip zu führen indem die

Abbildung 2. Hexagonale Anordnung von CABs.

Transkonduktanzverstärker der entsprechenden Zweige der CABs eingeschaltet werden.

Besondere Vorkehrungen müssen für die Umrandung der hexagonalen Struktur getroffen werden. Die IO-Buffer für die Kommunikation mit externen Bausteinen werden nahtlos an den Rändern des Arrays angebracht (hier: links und rechts) und sorgen für Ein- und Ausgang der zwei verbundenen CABs. Die unebenen Kanten haben eine Lage von CABs mit nur fünf verbundenen Nachbarn. Deswegen haben diese CABs einen unbenutzten Zweig (dargestellt mit einem Querstrich), der nur Dummy-Transistoren enthält, damit die wohldefinierte Eingangskapazität selbst an den Rändern aufrecht erhalten wird. CABs, die nicht für den Signalpfad benutzt werden, können komplett abgeschaltet werden, da ihre Kapazität nicht gebraucht wird.

#### Rekonfiguration

Jeder CAB hat 28 Bit Konfigurationsdaten, welche die Zustände der Schalter definieren. S-RAM am Rande des Arrays beinhaltet alle Konfigurationsdaten und kann von außerhalb des Chips durch eine digitale Logik angesteuert werden. Da kontinuierliche Signalverarbeitung ein Hauptmerkmal des Chips ist, ist es wünschenswert den Chip ohne Unterbrechung des analogen Signals zu rekonfigurieren. Der Filter wird ein Teil einer zeitkontinuierlichen Datenerfassung sein, deswegen sollte die Übertragungsfunktion so stetig wie möglich gemacht werden. Daher muss eine Technik angewendet werden, die es erlaubt neue Konfigurationsdaten im RAM im Voraus abzuspeichern und dann die Logik automatisch einen geeigneten Zeitpunkt finden zu lassen, um den neuen Zustand anzuwenden. Solch eine Technik wurde schon beschrieben (Reiser et al., 1999) und kann in den IO-Buffern implementiert werden.

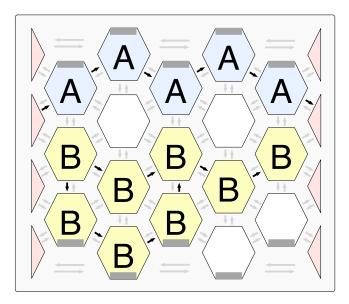

Abbildung 3. Zwei austauschbare Filter.

Um die Rekonfigurationseigenschaften des Chips zu verbessern gewährt die Logik volle oder teilweise Rekonfiguration. Eine Anwendung zeigt Abb. 3, in der zwei verschiedene Filterstrukturen A und B gleichzeitig auf dem Array realisiert sind. Idealerweise sind die erste und letzte Stufe der beiden Filter Nachbarn zu den gleichen IO-Buffern (Reihe 2 in diesem Beispiel). Während Filter A verbunden ist und arbeitet, kann ein anderer unverbundener Teil, hier durch Filter B dargestellt, rekonfiguriert werden. Nachdem der Filter B instantiiert ist, werden die Eingangs- und Ausgangsverbindungen an den IO-Buffern vom Filter A zu B geschaltet.

### 5 Design Beispiel

Ein Ziel des vorliegenden Designs ist, möglichst unterschiedliche Filterstrukturen realisieren zu können. Es wurde gezeigt, dass die hexagonal Struktur theoretisch die Geeignetste ist, um alle Typen von Rückkopplung und Verbindungen zu ermöglichen. Das folgende Beispiel wird darstellen, wie eine bekannte Filterstruktur praktisch realisiert werden kann.

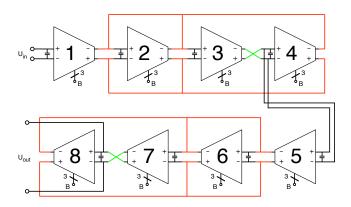

#### 5.1 Nutzbarkeit des Arrays für die Filterinstantiierung

Der Butterworth Filter 4. Ordnung in Biquad Anordnung, der von (Pavan and Tsividis, 2000) entworfen wurde, beinhaltet die gebräuchlichsten Designtechniken für das Filterdesign und stellt eine typische Anwendung für das Array dar. Wie man im Schaltplan in Abb. 4 erkennt, enthält es eine Rückkopplung 1. und 3. Ordnung, Signalinvertierung und parallele Verbindungen. Die Übersetzung in die Array Struktur in Abb. 5 ist eindeutig und zeigt perfekte Übereinstimmung.

## 5.2 Eine erste quantitative Untersuchung

Mit einfachen drei-Bit linear gewichteten  $G_m$ s, ähnlich wie in (Becker and Manoli, 2004) beschrieben, sind CABs

**Abbildung 4.** Beispiel eines Biquad Butterworth Filters 4. Ordnung.

mit Einheitsverstärkungsfrequenzen von 0 bis 250 MHz in 31 MHz Abständen in 0,18  $\mu$ m-Technologie möglich. Die Übersetzung des Butterworth Filters auf dem FPAA zeigt, dass es leicht auf 8 CABs aufgebaut werden kann. Da unbenutzte CABs komplett ausgeschaltet werden können, verbraucht dieses Filter voraussichtlich 94 mA, was zu einem Leistungsverbrauch von ungefähr 170 mW bei 1,8 V führt. Erste Simulationen in einer 0,18  $\mu$ m-Technologie wurden durchgeführt und bestätigen das vorgestellte Konzept.

# 6 Zukünftige Arbeit

Die grundlegenden Arbeiten über die Schaltungsebene (Becker and Manoli, 2004) und die vorliegende Arbeit über die Systemebene zeigen, dass ein praktikables Konzept für die rekonfigurierbare Instantiierung von zeitkontinuierlichen Analogfiltern in Hardware erstellt wurde. Die quantitativen Resultate wurden jedoch durch Berechnung mit Gleichungen in einem Modell erster Ordnung sowie mit sehr grundlegenden Simulationen erreicht.

Zukünftig müssen eine genauere Evaluation der Schaltung durchgeführt und einzelne Designparameter näher untersucht werden. Weiterhin werden auch Simulationen des entgültigen Design durchgeführt werden. Eine der zu bewältigenden Herausforderungen ist der Gebrauch von parasitären Eingangskapazitäten der CABs als integrierte Kapazitäten. Abhängig von der Vorspannung der Transistoren können die parasitären Eingangskapazitäten sehr nicht-linear sein und deswegen die Linearität des ganzen Filters verringern. Die Anforderungen an die Linearität sind für einen ersten Beweis des Konzepts nicht sehr hoch und es scheint vielversprechend, später Techniken zu evaluieren, die die Linearität der Transitorkapazitaten verbessern (Kraus et al., 2003).

Um die Richtigkeit des Konzeptes zu beweisen, ist die Fertigung des Designs in einem  $0.18\mu m$  CMOS Prozess geplant.

Abbildung 5. Instantiierung des Filters auf dem FPAA.

#### 7 Zusammenfassung

Es wurde eine Designmethode für digital programmierbare zeitkontinuierliche FPAAs präsentiert. Es ist ausdrücklich der rekonfigurierbaren Instantiierung von Analogfiltern gewidmet und ist daher sowohl bezüglich der Filterkoeffizienten als auch Filterstrukturen anpassungsfähig. Das Array besteht aus 17 CABs, welche aus  $G_m$ -Zellen aufgebaut werden, die das Signal durch den Chip leiten und auch formen. Die hexagonale Struktur des Arrays wurde vorgestellt und es wurde gezeigt, wie die wichtigsten Merkmale von zeitkontinuierlichen Filtern auf der Struktur abgebildet werden können. Intelligente IO-Buffer und partielle Programmierung wurden vorgeschlagen um möglichst kontinuierliche Signalverarbeitung sogar bei Rekonfigurierung zu erreichen. Anhand des Beispiels eines Butterworthfilters 4. Ordnung in Biquad Anordnung wurde die praktische Anwendbarkeit des Chips für reale Filterentwürfe dargestellt.

#### Literatur

Becker, J. and Manoli, Y.: A Continuous-Time Field Programmable Analog Array (FPAA) consisting of digitally reconfigurable G<sub>m</sub>-cells., IEEE International Conference on Circuits and Systems (ISCAS), 2004.

Kraus, W., Stelzig, B., Tille, T., and Schmitt-Landsiedel, D.: MOS Capacitances Used in Mixed-Signal Circuits and their Operative Range, Advances in Radio Sciences, Vol. 1, 295–299, 2003.

Nauta, B.: A CMOS Transconductance-C Filter Technique for Very High Frequencies, IEEE Journal of Solid-State Circuits, Vol 27, No. 2, 1992.

Pavan, S. and Tsividis, Y.: High Frequency Continuous Time Filters in Digital CMOS Processes, 2000.

Reiser, C., Znamirowski, L., Palusinski, O. A., B.K.Vrudhula, S., and Rakhmatov, D.: Dynamically reconfigurable analog/digital hardware - implementation using FPGA and FPAA technologies, J. Becker und Y. Manoli: FPAA-Architektur zur rekonfigurierbaren Instantiierung von zeitkontinuierlichen Analogfiltern 375

International Winter Conference of the Society For Computer Simulation (Scs), 1999.

Stojmenovic, I.: Honeycomb Networks: Topological Properties and Communication Algorithms, IEEE Transactions on parallel and distributed systems, 8, 1997.