# Eine präzise Multilevel-Testbench zur Systemsimulation und Charakterisierung einer 2,5 GHz PLL

# I. Kebaisy, F. Maibaum, M. Hinz, and B. Meinerzhagen

TU-Braunschweig, Institut für Elektronische Bauelemente und Schaltungstechnik (BST), Germany

**Zusammenfassung.** In diesem Aufsatz wird eine präzise Multilevel-Testbench zur PLL-Charakterisierung vorgestellt. Die Schwerpunkte dieses Beitrags sind einerseits das 10 GHz VCO-Design und andererseits die vorhersagefähigen Ergebnisse der mit Hilfe dieses Multilevelansatzes durchgeführten PLL-Systemsimulationen.

Bei dem VCO-Design wurden folgende Ergebnisse erreicht: Abstimmbereich  $\approx 26\%$  bzw. kvco $\approx 1300$  MHz/V, Phasenrauschen PN=-101,4 dBc/Hz @1 MHz Offset vom 10 GHz Träger, Leistungsverbrauch = 5,5 mW. Als realistisches Demonstrationsbeispiel ist das "analog mixed signal"Verhalten eines 2,5 GHz PLL-Systems für "dual-conversion"Strukturen bei IEEE 802.11a WLAN-Anwendungen gewählt worden. Für dieses Beispiel wird eine effiziente PLL-Modellierung kritischer PLL-Blöcke (Frequenzteiler und Phasenfrequenzdetektor) auf der Basis der PSS-Analyse und neuer Verilog-A/MS Befehle demonstriert. Die dabei verwendete Testbench kann im Prinzip in verschiedenen aktuellen Wireless Kommunikationssystemen bis 10 GHz wieder verwendet werden (Reuse-IP). Dieser Ansatz führt einerseits zur Verbesserung der Simulationszeiten (verglichen mit dem Transistorlevel) und andererseits zu genaueren und realistischeren Ergebnissen, vor allem am VCO-Ausgang (verglichen mit dem HDL-Level).

# 1 Einleitung

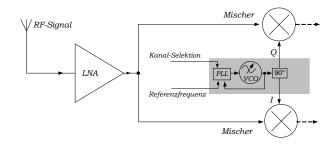

Das PLL-System ist ein wesentlicher Baustein in jedem mobilen HF-Front-End-Design. Es ist ein Kernsystem in allen modernen Transceivern (siehe Abb. 1) und dient dort in der Regel zur Frequenz-Synthese (Best, 1999).

Aufgrund der ständig steigenden PLL-Komplexität (Transistorenzahl) ist eine PLL-Simulation auf dem Transistorlevel kaum praktikabel, deshalb werden die PLL-

Correspondence to: I. Kebaisy (i.kebaisy@tu-bs.de)

Abb. 1. Die PLL als Kernsystem.

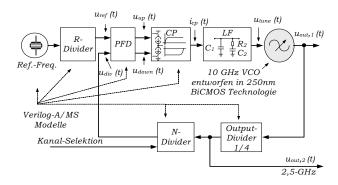

Transistorblöcke zurzeit einzeln untersucht bzw. eine komplette PLL-Systemsimulation wird lediglich auf dem HDL-Level, meistens ohne HF-Ausgangssignal, durchgeführt (Kebaisy and Hinz, 2003; Hinz, 2002). Beide Ansätze haben jeweils ihre Schwächen. Abbildung 2 veranschaulicht unsere Multilevel Testbench. Hier ergänzen sich HDL-Modelle und ein VCO-Modell auf dem Transistorlevel zu einem vollständigen PLL-System.

# 2 Designumgebung und Technologie

Als Designumgebung wird in dieser Arbeit das *IC.5.10.41* von Cadence mit dem Schaltkreissimulator *SpectreRF* verwendet (Cadence Design System, 2005), der die Verhaltensbeschreibungssprache *Verilog-A/MS* unterstützt (Cadence Design System, 2004). Für den Entwurf des VCO auf der Transistorebene wird das Design-Kit SG25VD von *IHP* verwendet. Es handelt sich hierbei um eine 250 nm BiCMOS-Technologie. Diese Technologie ist auf die Entwicklung von "silicon-based" Mikrowellenschaltungen, HF-Blöcken und Transceivern bis 124 GHz und SoC Applikationen fokussiert (IHP Homepage).

Abb. 2. Multilevel PLL-Testbench.

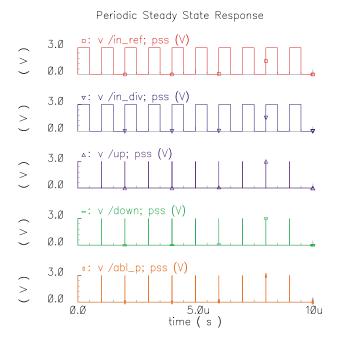

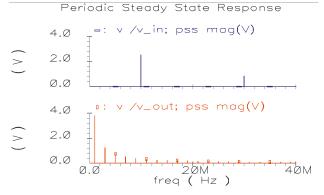

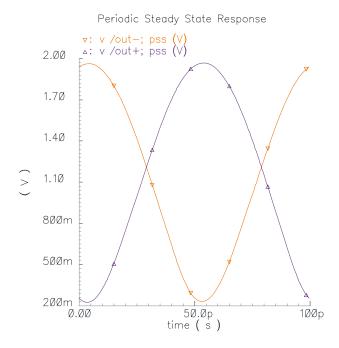

**Abb. 3.** Eingangs- und Ausgangssignale des PFD im periodischen eingeschwungenen Zustand für 1 MHz Referenzfrequenz und 1 nsec ABL-Breite

#### 3 Highlights zu dieser PLL-Modellierung

Eine Verhaltensbeschreibung der "Transceiver" bzw. der PLL-Blöcke, vor allem des Phasenfrequenzdetektors (PFD) und des Frequenzteilers, bringt eine signifikante Zeit- und Speicherplatzersparnis mit sich (Kundert and Zinke, 2004; Kebaisy et al., 2006), wobei die grundsätzliche Funktionalität des Blocks erhalten bleibt. In diesem Beitrag werden erstmals PLL-Simulationsergebnisse, mit Hilfe der neu unterstützten Befehle (\*instrument\_module\*) und (\*ignore\_state\*) (Cadence Online-Dokumentation/Sourcelink) veröffentlicht. Durch deren Anwendung wird der "hiddenstates checker" in der PSS-Analyse deaktiviert und somit die störende Fehlermeldung, die das Durchführen einer PSS-Analyse verhindert, beseitigt. Dieses ermöglicht im

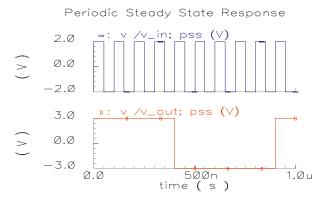

**Abb. 4.** Eingangs- und Ausgangssignale des Freq.-Teilers im Zeit-(oben) und Freq.-Bereich (unten).

Vergleich zu (Hinz, 2002; Kundert, 2006) eine einfache und effiziente Modellierung. Dieser Ansatz birgt aber die Gefahr in sich, dass durch nicht erkannte "hidden-states" die PSS-Analyse verfälscht wird. Um diese Gefahr für dieses Beispiel auszuschließen, wurde der Ansatz durch eine aufwändige transiente Simulation verifiziert. Daraus ergab sich, dass für das vorliegende Beispiel die PSS-Analyse ohne Probleme konvergiert und genaue Ergebnisse liefert. Folgende transistornahe Effekte werden in dieser PLL-Testbench und in den Verhaltensmodellen berücksichtigt:

- 1. Die Spannungsabhängigkeit des Ausgangsstroms in der Ladungspumpe (CP) (Kebaisy and Hinz, 2003).

- 2. Ein PSS-tauglicher PFD Type-4 mit einstellbarer Breite der "Anti-Backlash"Pulse (ABL) wurde modelliert, welcher auf minimale Phasenunterschiede reagiert und dementsprechend keine "Tote Zone" aufweist (siehe Abb. 3).

- 3. Ein passives Loop-Filter bestehend aus drei Elementen wurde verwendet.

Abbildung 4 zeigt die Ergebnisse der PSS-Analyse für den Frequenzteiler im Zeit- und Frequenzbereich bei einer Eingangsfrequenz  $f_{\text{in}}$ =10 MHz und einem Teilerverhältnis

Abb. 5. LC-Oszillator-Prinzip.

*R*=10. Die Funktionalität der PSS-Analyse bei größeren Teilerverhältnissen wurde ebenso getestet und es zeigten sich keine Probleme.

Unter Berücksichtigung der unter 1)–3) aufgeführten wichtigen Effekte in der PLL-Testbench, ergibt sich als Ergebnis eine Steuerspannung, deren Genauigkeit derjenigen weitgehend entspricht, die sich durch eine vollständige Modellierung auf der Transistorebene erzielen lässt.

## 4 10 GHz CMOS-VCO-Design

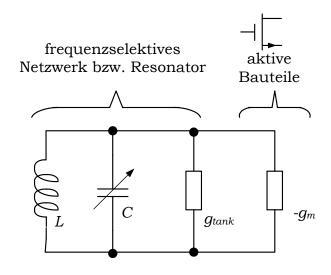

Zur Bestimmung der Ausgangsfrequenz wird im Prinzip ein frequenzselektives Netzwerk benötigt, dessen Verluste kompensiert werden müssen. Dies entspricht in grober Nährung dem in Abb. 5 gezeigten Ersatzschaltbild. Für die Kompensation werden aktive Bauteile benötigt. Diese kompensieren die durch  $g_{\text{tank}}$  verursachte Verlustenergie.

Für den CMOS-VCO im 10 GHz Bereich wurde eine ähnliche Topologie wie in (Herzel et al., 2003; Gustat et al., 2003) mit zwei kreuzgekoppelten NMOSTs ausgewählt (siehe Abb. 6) und komplett für den 10 GHz Bereich neu dimensioniert, untersucht und optimiert. Diese Topologie wurde vor allem bevorzugt, weil ein solcher VCO hohe Frequenzen bis 13 GHz erzeugen kann. Die Designkonzepte von (Hajimiri and Lee, 1999; Sadat et al., 2005; Razavi, 2001; Shu and Sanchez-Sinencio, 2005) wurden dabei berücksichtigt.

# 4.1 Charakterisierung der MOSTs im Design-Kit

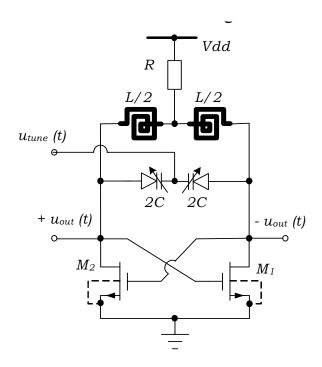

Die Transitfrequenzen der zur Verfügung stehenden MOSTs liegen bei 40 GHz (NMOS) bzw. 16,5 GHz (PMOS). Diese Charakterisierung wurde jeweils bei mittleren DC-Spannungen ( $U_{ds}$ ,  $U_{gs}$ ), minimaler Gate-Länge

Abb. 6. Topologie des verwendeten differentiellen VCO.

$L_{\text{min}}$ =240 nm und einer Breite von W=10  $\mu$ m ermittelt. Die Abschätzung erfolgte nach der Formel (Lee, 2004):

$$f_T \approx \frac{g_m}{2\pi \left(C_{gs} + C_{gd}\right)} \tag{1}$$

Eine genauere Untersuchung der Kleinsignalkurzschluss-Stromverstärkung über dem gesamten Bereich der Gate-Source-Spannung wurde unter den gleichen Rahmenbedingungen durchgeführt und hat die o.g. Ergebnisse mit einer kleinen Abweichung von ca. 4% bestätigt (siehe Abb. 7). Die Ermittlung erfolgt jeweils bei dem Nulldurchgang nach der Formel:

$$\underline{H}_{21} = \frac{\underline{I}_2}{\underline{I}_1} \Big|_{\underline{U}_2 = 0} = 0 [dB] \tag{2}$$

#### 4.2 Charakterisierung des Varaktors

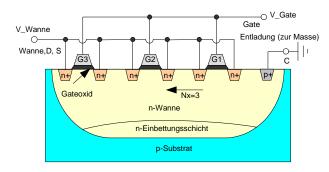

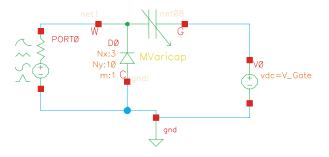

Das Design-Kit enthält einen speziellen MOS-Varaktor (IHP Design-Kit Dokumentation, 2006). Die Gesamtkapazität ist proportional zur Anzahl der Gates in x- und y-Richtung, also zu  $N_X$  und  $N_Y$  (siehe Abb. 8).

Die Steuerspannung *V\_Wanne* wird an den n+-Wannenkontakten angeschlossen (siehe Abb. 9). Die Gate-Spannung *V\_Gate* beträgt 2,5 V.

Nach einer S-Parameter-Analyse bei  $10\,\mathrm{GHz}$  und einem "sweep" der Steuerspannung  $V_-Wanne$  werden die

**Abb. 7.**  $f_T$  des NMOS über  $U_{gs}$ .

**Abb. 8.** Varaktor-Querschnitt für Nx=3.

S-Parameter in Z-Parameter umgerechnet und daraus die Kapazität nach (3) bzw. der Gütefaktor nach (4) bestimmt.

$$C = \frac{-1}{2\pi f.\Im\left\{\underline{Z}_C\right\}} \tag{3}$$

$$Q = \frac{-\Im\left\{\underline{Z}_C\right\}}{\Re\left\{\underline{Z}_C\right\}} = \frac{1}{2\pi f.CR} \tag{4}$$

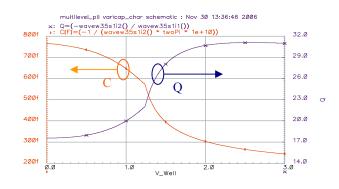

Die C - V - und Q - V -Kurven des Varaktors sind in Abb. 10 zu sehen.

Aus Abb. 10 lässt sich erkennen, dass die Varaktor-Güte und die Kapazität stark von der Steuerspannung abhängen. Diese Abhängigkeit ist monoton. Mit steigender Steuerspannung wird die Varaktor-Kapazität kleiner,  $C_{\rm max}/C_{\rm min}{\approx}3$ . Daher ist mit einem großen Abstimmbereich des VCO zu rechnen. Die Güte wird im betrachteten Steuerspannungsbereich nicht kleiner als 18. Somit kann ebenfalls mit einer hinreichend großen VCO-Ausgangsamplitude gerechnet werden.

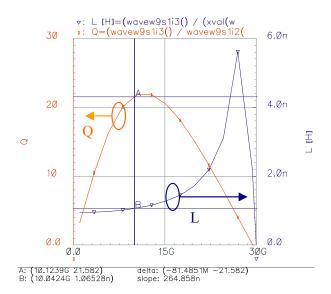

### 4.3 Charakterisierung der Spulen

Da die untersuchten rf-NMOSTs eine hohe Transitfrequenz von ca. 38 GHz haben, wird die maximal erreichbare Oszillatorfrequenz wesentlich von den im Design-Kit verfügbaren Induktivitäten bestimmt, die unterhalb ihrer eigenen Re-

Abb. 9. Varaktor-Testbench.

**Abb. 10.** C - V - und Q - V -Kurven über der Steuerspannung V\_Well. Simuliert bei: Nx=3, Ny=10,  $V\_Gate=2,5$  V @ 10 GHz.

sonanzfrequenz betrieben werden müssen, also in demjenigen Frequenzbereich in dem die parasitären Kapazitäten das Verhalten nicht dominieren. Unsere Untersuchungen haben ergeben, dass Resonanzfrequenzen bis 29 GHz ausreichen. Dafür eignet sich die kleinste verfügbare Induktivität L=0,94 nH am besten. In Abb. 11 ist ihre Charakterisierung dargestellt, wobei L und Q mit den Formeln (5) und (6) bestimmt wurden:

$$L = \frac{\Im\left\{\underline{Z}_L\right\}}{2\pi f} \tag{5}$$

$$Q = \frac{\Im\left\{\underline{Z}_L\right\}}{\Re\left\{\underline{Z}_L\right\}} \tag{6}$$

Abbildung 11 zeigt auch, dass bei  $f=10\,\text{GHz}$  diese Induktivität den Wert 1 nH hat und die Güte ihr Maximum von ca. 21,5 erreicht.

## 5 VCO-Simulationsergebnisse

Die Varaktoren und Transistoren wurden so dimensioniert und optimiert, dass sich der Entwurf in Abb. 6 nun für 10 GHz eignet. Ein besonderes Augenmerk wurde dabei auf minimalen Leistungsverbrauch und geringes Phasenrauschen

**Abb. 11.** L und Q über der Frequenz für L=0,94 nH.

Abb. 12. Diff-Ausgänge des VCO.

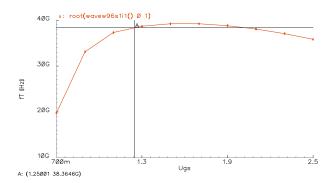

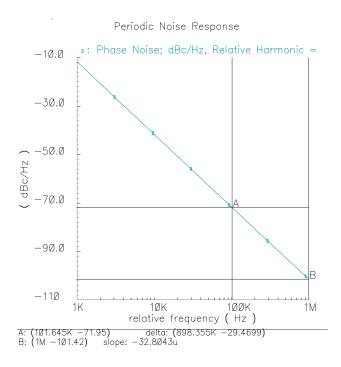

gerichtet. Der VCO zieht einen Strom von 2,2 mA von einer 2,5 V Betriebsspannung und somit liegt der Leistungsverbrauch bei Pdc = 5,5 mW. In Abb. 12 sind die differentiellen VCO-Ausgänge im periodisch eingeschwungenen Zustand bei 10 GHz zu sehen.

Wie erwartet, hat die Grundwelle eine höhere Amplitude "rail-to-rail" von ca. 70% der Betriebsspannung erreicht und somit konnte ein guter Wert für das Phasenrauschen von

**Abb. 13.** VCO-Phasenrauschen simuliert über dem Träger-Abstand für  $f_c$ =10 GHz.

PN=-101@1 MHz "Offset" erzielt werden (siehe Abb. 13).

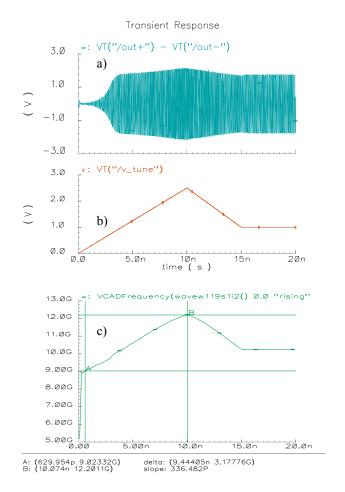

Den Effekt der Steuerung auf die VCO-Ausgangsfrequenz und die Ermittlung des Abstimmbereiches zeigt Abb. 14. Aus Abb. 14b und c erkennt man, dass der VCO einen großen Frequenzabstimmbereich von ca. 3177 MHz und ein hohes "VCO-Gain" von ca. kvco≈1300 MHz/V hat. Ein Vergleich mit aktuellen Veröffentlichungen für gemessene 10 GHz VCOs ist in Tabelle 1 aufgelistet. Die in dieser Arbeit erreichten Kenngrößen liefern vergleichbare Ergebnisse, vor allem wenn es auf einen guten Kompromiss zwischen allen Kenngrößen ankommt.

# 6 PLL-Simulationsergebnisse

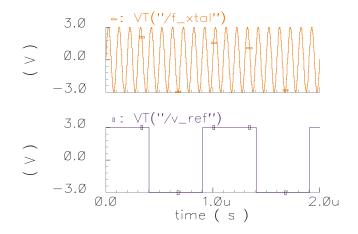

Die Multilevel PLL-Testbench wurde nun nach Abb. 2 aufgebaut. Um eine realistische Demonstration zu gewährleisten, wurden die PLL-Parameter an das Heterodynkonzept einer IEEE 802.11a WLAN-Anwendung angepasst. Diese PLL-Struktur erlaubt nach geringfügiger Änderung auch den Einsatz in "direct-conversion"Strukturen, indem die VCO-Ausgangsfrequenz durch zwei (statt vier) dividiert wird. Abbildungen 15, 16 zeigen die Simulationsergebnisse des untersuchten PLL-Systems.

Bei Anlegen einer geeigneten Anfangsspannung an die Ausgangskapazität des Loop-Filters stellt sich eine VCO-Steuerspannung von ca. 850 mV ein (siehe Abb. 16a) und der VCO schwingt schnell auf einer Frequenz von ca. 10 GHz ein (siehe Abb. 16b und c).

**Abb. 14.** (a) VCO-Diff.-Ausgang im Zeitbereich, (b) Steuerspannung und (c) die entsprechende Ausgangsfrequenz.

Tabelle 1. Vergleich mit aktuellen Veröffentlichungen.

| 10 GHz VCO "state-of-the-art" |                         |                                     |                          |

|-------------------------------|-------------------------|-------------------------------------|--------------------------|

| Design                        | P <sub>dc</sub><br>[mW] | PN @<br>1 MHz<br>Offset<br>[dBc/Hz] | Δf [GHz]                 |

| diese Arbeit                  | 5,5                     | -101,4                              | 9–12,2<br>≈26%           |

| Titus et al. (2006)           | 27                      | -112                                | 8-12                     |

| Dongkyu et al. (2006)         | 0,72                    | -108                                | 13,6 %                   |

| Tae-young et al. (2005)       | 49,94                   | -125,33                             | 10,2−<br>12,48<br>≈20,1% |

| Axelrad et al. (2005)         | 26                      | -104                                | 10,2−13<br>≈25%          |

**Abb. 15.** 10 MHz Ausgangssignal des Kristalloszillators (oben), Ausgangssignal des *R-Dividers* bzw. das 1 MHz PLL-Referenzsignal (unten).

Abb. 16. (a) VCO-Steuerspannung, (b) VCO-Diff-Ausgang und (c) VCO-Frequenz.

Die 5  $\mu$ sec-abdeckende Transientanalyse wurde auf einem Linux-PC mit 4 AMD (Opteron) Prozessoren, Taktfrequenz von 2 GHz und 8 GB Speicher durchgeführt. Die benötigte Simulationszeit lag bei 6 min und der benötigte Speicherbedarf lag bei 3,4 GB.

## 7 Zusammenfassung und Ausblick

Es wurde eine Multilevel Testbench für eine PLL-Systemsimulation vorgestellt, die darauf zielt den bestmöglichen Kompromiss zwischen Simulationsgenauigkeit und Simulationszeit zu erzielen. Der für die Genauigkeit des HF-Ausgangssignals kritische Block, also der spannungsgesteuerte Oszillator (VCO), wurde auf der Transistorebene simuliert. Die anderen Blöcke wurden durch präzise Verhaltensmodelle beschrieben. Für die PLL-Verhaltensmodelle konnte eine effiziente PSS-Analyse aufgrund neuer Verilog-A/MS-Befehle durchgeführt werden, deren Genauigkeit durch eine aufwändige Transientanalyse verifiziert wurde. Die Verwendung der Verhaltensmodelle bewirkt eine große Speicherplatz- und Rechenzeitersparnis, wodurch solche PLL-System-Simulationen erst ermöglicht werden.

Ein 10 GHz CMOS-VCO-Design in 250 nm Technologie für den Einsatz in verschiedenen Wireless Anwendungen wurde präsentiert. Die dabei erzielten Werte für die Kenngrößen Leistungsverbrauch, Phasenrauschen und Abstimmbereich entsprechen dem Stand der Technik, wie ein Vergleich mit der aktuellen Literatur ergeben hat.

Die hier vorgestellten Untersuchungen dienen vor allem dazu, ein vorhersagefähiges "top-down-design" bei der Charakterisierung einer PLL zu unterstützen und später die erforderliche Optimierung ohne großen Aufwand zu ermöglichen.

Danksagung. Wir bedanken uns beim IHP-Microelectronics-Team, Frankfurt (Oder)-Germany, für die Unterstützung bezüglich des Design-Kits und auch bei unseren Kollegen bei Nokia Research Center, Bochum-Germany, für den wertvollen Informationsaustausch und Bereitstellung der PLL-Parameter im Rahmen des BMBF-Projekts HGDAT im Jahre 2003. Ein letzter Dank geht an A. Kuligk und R. Kamitz, TU-Braunschweig, BST, für ihre Unterstützung.

## Literatur

- Axelrad, D., de Foucauld, E., and Boasis, M.: A multi-phase 10 GHz VCO in CMOS/SOI for 40 Gbits/s SONET OC-768 clock and data recovery circuits. Radio Frequency integrated Circuits (RFIC) Symposium, 2005. Digest of Papers. 2005 IEEE, 12-14 June 2005, 573–576, 2005.

- Best, R.: Phase-Locked Loops, Design, Simulation, And Applications. New York: Mc Graw-Hill Companies, Inc, Fourth Edition 1999.

- Cadence Design Systems: SpectreRF Simulation Option User Guide Product Version 5.1.41 San Jose: Cadence Design Systems, Inc., July 2005.

- Cadence Design Systems: Cadence Verilog-A Language Reference Product Version 5.4. San Jose: Cadence Design Systems, Inc., November 2004.

- Cadence Onlie-Dokumentation (Sourcelink): http://sourcelink.cadence.com.

- Dongkyu, P. and Byunghoo, J.: Low power LC-VCO design using direct cross-coupled cell biasing. Circuits and Systems, 2006. IS-CAS 2006. Proceedings. 2006 IEEE International Symposium on 21-24 May 2006, 4 pp., 2006.

- Gustat, H. and Herzel, F.: Integrated FSK demodulator with very high sensitivity. Solid-State Circuits, IEEE J. Solid-State Circuits, 38(2), 357–360, 2003.

- Hajimiri, A. and Lee, T. H.: Design issues in CMOS differential LC oscillators Solid-State Circuits, IEEE J. Solid-State Circuits, 34(5), 717–724, 1999.

- Herzel, F., Fischer, G., and Gustat, H.: An integrated CMOS RF synthesizer for 802.11a wireless LAN. Solid-State Circuits, IE-EE J. Solid-State Circuits, 38(10), 1767–1770, 2003.

- Hinz, M.: A Novel Nonlinear Multi-Level Model for PLL. Analog 2002, IMM/ITG Workshop, Bremen, 2002.

- IHP Homepage. Innovation for High Performance micro electronics: http://www.ihpffo.de/.

- IHP-Design-Kit Dokumentation, interne Mitteilung, 2006.

- Kebaisy, I. und Hinz, M.: Evaluation der Referenzunterdrückung einer auf Verhaltensebene modellierten Phasenregelschleife mittels Transienten- oder Periodic Steady State Analyse. Konferenz-Einzelbericht, GMM Fachbericht. "11. E.I.S. – Workshop: Entwurf Integrierter Schaltungen und Systeme" Erlangen, 2003.

- Kebaisy, I., Domann, S., and Meinerzhagen, B.: Präzise Modellierung und Parameteranpassung eines 5,2 GHz LNA für WLAN-Anwendungen. Konferenz-Einzelbericht: GMM Fachbericht "9. MBMV06-Workshop: Methoden und Beschreibungssprachen zur Modellierung und Verifikation von Schaltungen und Systemen" Dresden, 2006.

- Kundert, K. and Zinke. O.: The Designer's Guide to Verilog-AMS. Kluwer Academic Publishers, 2004.

- Kundert, K.: Hidden State in SpectreRF, http://www.designers-guide.com, Mai 2006.

- Lee, T. H.: The Design of CMOS Radio-Frequency Integrated Circuits, Cambridge University Press, 2004.

- Razavi, B.: Design of Analog CMOS Integrated Circuits. McGraw-Hill. 2001

- Sadat, A., Yi Liu, Chuanzhao, and Yu Yuan, J. S.: Analysis and modeling of LC oscillator reliability. Device and Materials Reliability, IEEE Transactions on Device and Materials Reliability, 5(1), 119–126, 2005.

- Shu, K. and Sanchez-Sinencio, E.: CMOS PLL SYNTHESIZERS, Analysis and Design. Springer Science + Business Media Inc., 2005.

- Tae-young, Choi, Hanil, L., Katehi, L. P. B., and Mohammadi, S.: A low phase noise 10 GHz VCO in 0.18/spl mu/m CMOS process. Wireless Technology, 2005. The European Conference on 3–4 Oct. 2005, 273–276, 2005.

- Titus, W. S. and Kenney, J. G.: 10 GHz VCO for 0.13/spl mu/m CMOS Sonet CDR. Radio Frequency Integrated Circuits (RFIC) Symposium, 2006 IEEE 11-13 June 2006, 4 pp., 2006.